电压降及缓解技术IP介绍

目录

1. 电压降及缓解技术介绍

1.1 系统电源分配网络(PDN)与电压降

1.2 当前的被动式电压降缓解方法

1.3 用于动态电压降缓解的自适应时钟技术

2. 自适应时钟分配分析

2.1 电压降检测期间的电压降分析

2.2 最坏情况电压降缓解电压及最小电压(Vmin)节省

2.3 传统时钟多路复用器方法的示例分析

2.3.1 最大化最小电压(Vmin)节省

3. 集成式电压降响应解决方案

3.1 Aeonic Insight™ 电压降检测器

3.2 Aeonic Generate™ AWM3

3.3 靶向电压降遥测

4. 结论

1. 电压降及缓解技术介绍

电压降是高性能系统级芯片(SoC)中日益受到关注的问题。本白皮书探讨了主动式电压降缓解解决方案的相关考量因素,将讨论电压降的影响、缓解技术,以及自适应时钟解决方案的应用详细分析。

1.1 系统电源分配网络(PDN)与电压降

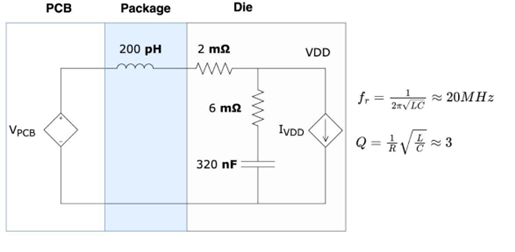

电源分配网络(PDN)通常始于系统中的电压调节器,流经带有大量去耦电容的印刷电路板(PCB)电源层,最终连接到封装并向芯片上的凸点输送电流。电源分配网络中最高的阻抗通常源于芯片电容和封装电感,从而产生5至100兆赫兹(MHz)量级的谐振。考虑图1中的简化RLC电路,其中片上电容和电感产生约20兆赫兹的谐振频率。存在向芯片输送电流的串联电阻,且芯片上的电容中存在寄生电阻。品质因数(Q-factor)决定了振荡衰减的速度。

图1. 电源分配网络模型示例

在SPICE仿真中,向电路施加6.5安培(A)的瞬时负载。电流的急剧变化会导致系统中出现较大的电压降(芯片处电压降超过15%),因为电感会阻碍电流的变化。随后,随着系统稳定,电压降约为5%。当发生电压降时,逻辑门的驱动能力下降,会增加其传播延迟并削弱时序裕量。在某些情况下,时序约束将被违反,系统内可能出现逻辑错误。因此,必须缓解电压降以确保系统级芯片(SoC)的正常运行。

1.2 当前的被动式电压降缓解方法

系统级芯片(SoC)设计中通常会包含一定程度的被动式缓解措施。功率与性能之间始终存在权衡关系。增加功率和降低性能可以减轻电压降的影响,但这通常与降低功率、提高性能的设计目标相悖。

- 提高最小电压(Vmin)—— 一种方法是提高电压水平。这使系统能够在电压降事件期间维持其时序裕量和正常运行。然而,这种方法也存在不良副作用:由于始终使用更高的电源电压,会增加功耗,而电压降事件本应是罕见的。

- 降低时钟频率—— 降低时钟频率可以增加可用的时序裕量,但这种方法也会降低性能。

- 增加去耦电容—— 去耦电容有助于减轻L×di/dt效应,但会占用芯片面积并增加成本。

上述被动式技术一旦设计到系统级芯片(SoC)中,就会始终处于工作状态,且每种技术都会以不同方式对性能产生负面影响。相比之下,电压降事件是间歇性且罕见的。自适应时钟缓解解决方案可在电压降事件期间提供缓解,并能够降低最小电压(Vmin),从而节省功耗。

1.3 用于动态电压降缓解的自适应时钟技术

自适应时钟解决方案提供两项基本功能:

- 通过维持时序裕量来保证系统功能正常。

- 实现最小电压(Vmin)降低和功耗节省。

为实现这些功能,自适应时钟解决方案需执行三项基本操作:

- 检测电压降。

- 快速降低时钟频率以提供充足的时序裕量。

- 随着电压恢复,智能地恢复时钟频率。

要实现自适应时钟,需满足五项关键要求:

- 可观测性—— 需对电源分配网络(PDN)和电压降行为进行分析和数据记录,以了解电源分配网络(PDN)的片上行为,从而使自适应时钟能够适应并优化后硅实际情况。

- 快速检测和适应时间—— 检测速度越快越好。快速的检测和适应时间使系统能够缓解幅度更大、速度更快的电压降事件。系统对电压降事件的响应速度越快,可实现的最小电压(Vmin)节省就越多。

- 自适应时钟频率管理—— 这需要以适当但不过度激进的方式降低频率,以最大限度减少对性能的影响。同时,随着电压恢复,以平稳、渐进的方式恢复工作频率,最大限度降低自感应电压降的风险。

将自适应方法与简单的时钟频率二分频解决方案进行比较:在许多情况下,如此大幅的频率降低过于激进。在电压恢复前以半速运行时钟会导致显著的性能损失。此外,当电压恢复时,突然取消二分频,在电流负载突然恢复的情况下,可能会自感应产生另一个L×di/dt电压降事件。

- 灵活且可编程的电压降响应—— 在前硅分析中,通过广泛的电源分配网络(PDN)分析来预测电源分配网络(PDN)行为和潜在电压降曲线较为复杂,且无法考虑工作负载变化、空间变异性或工艺角。后硅可编程性提供了适应实际系统级芯片(SoC)行为的灵活性,是必不可少的特性。

- 集成性—— 集成了电压降检测的自适应时钟频率管理器能够提供最佳的系统级解决方案。

- 自适应时钟分配分析

自适应时钟系统分析评估了可防护的电压降幅度和严重程度,以及可实现的最小电压(Vmin)节省。

实际电压降通常呈正弦曲线形状,其斜率在电压降开始和结束时较平缓,在中间时最陡峭。电压降分析的一阶模型假设电压降以恒定速率发生,这一假设简化了分析过程。

以下分析考虑两项指标:

- 电压降检测时的电压。

- 系统对检测到的电压降做出响应期间发生的电压降。

电压降检测时的电压受期望阈值、检测时间或采样率以及电压降检测器精度的影响。

系统响应期间的电压降是以下因素的函数:

- 从电压降检测器到时钟源控制逻辑的传播延迟。

- 降低时钟频率所需的时间。

- 时钟树插入延迟

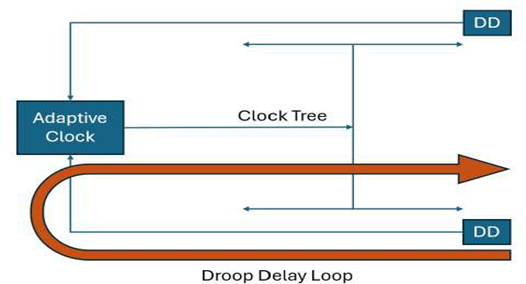

图2. 系统适应时间(T_adapt)由环路延迟决定

适应时间由以下公式定义:

T_adapt = T_detect + T_prop_delay + T_response + T_clk_insertion

其中:

- T_detect(检测时间):检测器采样周期与电压降检测器内部组合逻辑延迟之和。

- T_prop_delay(传播延迟):电压降断言信号从电压降检测器模块输出传输到自适应时钟源的飞行时间或传播延迟。

- T_response(响应时间):电压降断言到达自适应时钟发生器至产生较慢时钟边沿的时间。

- T_clk_insertion(时钟插入延迟):时钟边沿从自适应时钟发生器通过时钟树传播到逻辑中的时钟接收端所需的时间。

2.1 电压降检测期间的电压降分析

检测期间的电压降分析确定了此阶段发生的最坏情况电压降以及电压降检测器输出断言时的系统电压。

假设电压以恒定速率下降,电压检测期间的电压降(V_detect)由以下公式描述:

V_detect = R × T_detect

其中:

- R = 电压降速率,单位为毫伏/纳秒(mV/ns)

- T_detect(检测时间):如上文定义的检测器采样周期之和

在T_detect期间,电压下降V_detect。要确定电压降检测器输出断言时的最坏情况系统电压,还需考虑电压降检测器精度和电压降阈值电压。

电压降阈值电压是电压降检测器输出断言时的电压。该阈值会受到电压降检测器精度的影响。如果精度为±10毫伏(mV),则在最坏情况分析中,应假设实际电压比设定阈值低10毫伏(mV)。另一个因素是电压降检测时间,其取决于电压降检测器架构,范围可能从数百皮秒(ps)到数纳秒(ns)。

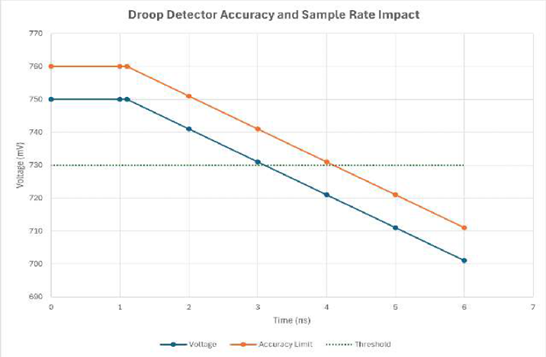

考虑图3所示示例。在此示例中,期望阈值设定为730毫伏(mV),电压降速率为10毫伏/纳秒(mV/ns)。此外,采样率为1吉赫兹(GHz),采样时间点如图表中的点所示,分别为1纳秒(ns)、2纳秒(ns)、3纳秒(ns)等。电压降检测器的精度为±10毫伏(mV)。蓝线表示实际电压,红线表示电压降检测器的+10毫伏(mV)精度极限。

图3. 电压降检测器精度和采样率的影响

- 在3纳秒(ns)时,实际电压略高于阈值,无电压降断言输出。

- 在4纳秒(ns)时,实际电压低于阈值,但如果考虑最坏情况精度(+10毫伏(mV)),检测到的电压仍高于阈值,电压降检测器不输出断言。

- 在5纳秒(ns)时,即使考虑传感器的任何不准确性,电压仍低于阈值,将产生电压降断言。

实际电压约为710毫伏(mV),比期望阈值低20毫伏(mV)。这20毫伏(mV)由两部分组成:10毫伏(mV)源于电压降检测器的精度,10毫伏(mV)源于采样周期T_detect期间的电压降。如果电压降检测器输出端存在时钟到输出(clock-to-q)延迟或其他组合逻辑延迟,实际电压将略低。

如果电压降检测器是模拟式且持续检测,则仍需考虑最坏情况精度,但只要最坏情况精度低于阈值,即可立即产生电压降断言,而无需等待离散采样点低于阈值。如图3所示,电压降断言将在4纳秒(ns)后立即发生,此时电压约为720毫伏(mV)。

电压降检测器输出断言时的实际系统电压将是阈值电压减去电压精度误差再减去V_detect,如图所示。

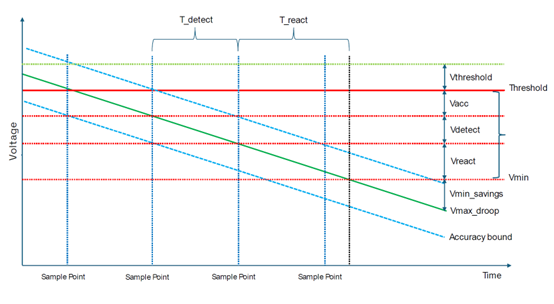

2.2 最坏情况电压降缓解电压及最小电压(Vmin)节省

在此示例中,结合总系统适应时间和电压降检测器精度,计算潜在的最小电压(Vmin)节省和系统可缓解的最坏情况电压降

图4. 潜在最小电压(Vmin)节省计算

阈值电压Vthreshold定义为相对于额定工作电压的下降电压。例如,如果额定电压V_nom为750毫伏(mV),则V_threshold可设定为35毫伏(mV)。这将理想的电压降断言电压设定为715毫伏(mV)。

根据上述定义,电压降检测器输出断言时,相对于阈值的最坏情况电压降(V_droop_wc)定义为:

V_droop_wc = V_acc + V_adapt

其中:

- V_adapt = T_adapt × R

- V_acc是与电压降检测器相关的电压精度误差。

如上文所述,一旦确定V_droop_wc,即可计算考虑检测时和系统响应期间电压降后的潜在最小电压(Vmin)节省,公式如下:

V_min_savings = V_max_droop - V_threshold - V_droop_wc

其中:

- V_max_droop(最大电压降)是系统中预期的最大电压降或允许的最大电压降,相对于额定工作电压测量。

- V_threshold(阈值电压)是在电压降检测器中设定的阈值点。

主动缓解系统可防护的最大电压降可通过相同公式推导得出:将V_min_savings设为0并重新整理:

V_max_droop = V_threshold + V_droop_wc

V_max_droop = V_threshold + V_acc + R × (T_adapt)

要最大化潜在的最小电压(Vmin)节省,或最大化系统可缓解的电压降,需要优化上述公式中的参数。

环路延迟T_adapt部分受电路尺寸、电压降断言信号的飞行时间和时钟树插入延迟的限制。通过将自适应时钟源尽可能靠近其服务的逻辑,可以潜在地改善这一情况。这使得T_response成为唯一可最小化的其他变量。采用最先进的自适应时钟(能够接收异步电压降断言输入并快速降低时钟频率)是最小化T_adapt的明确选择。如果需要时钟多路复用器,若需要时钟域交叉电路,T_response时间将增加多个周期。

通过提高采样率或提高电压降检测器的精度,可以最小化V_detect。选择适当的V_threshold至关重要:如果阈值电压设定过高,在电源的正常工作负载噪声期间,电压降响应将被过于频繁地触发;如果阈值电压设定过低,在发生最坏情况电压降时,系统将无法及时响应以防止时序故障。

2.3 传统时钟多路复用器方法的示例分析

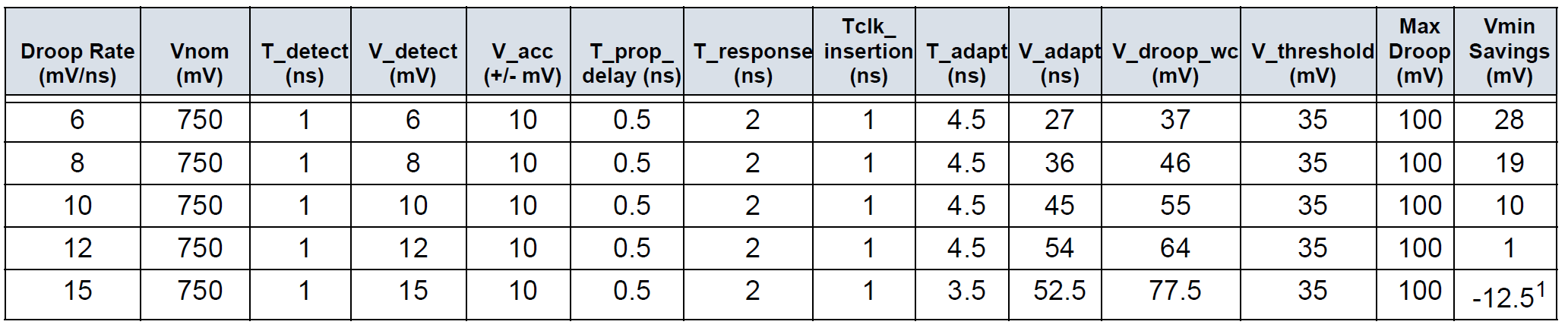

时钟多路复用是指设计人员通过多路复用或切换两个时钟信号来实现电压降缓解的技术。一个时钟分配工作频率,另一个用于提供安全频率。表1展示了不同电压降速率下的上述分析结果。

表1. 传统时钟多路复用器分析

¹ 此列中的负数表示在指定条件下无法缓解此类幅度的电压降。

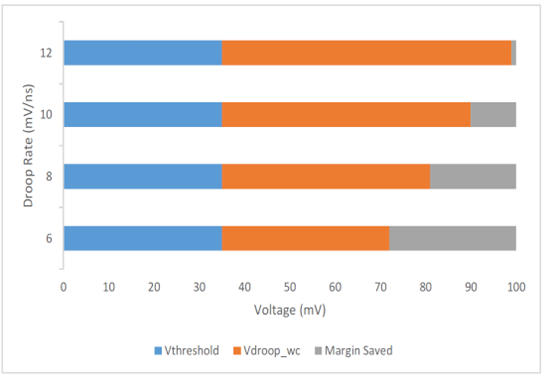

此示例展示了2G赫兹(GHz)系统时钟使用需要多个时钟域交叉同步级的时钟多路复用器时的典型值。T_adapt为4个时钟周期(500皮秒×4个周期)。T_response时间在整个检测和响应期间的电压降中占主导地位。12毫伏/纳秒(mV/ns)、深度100毫伏(mV)的电压降可被缓解,并有助于防止严重的时序故障。图5展示了最坏情况电压降与节省裕量之间的关系。

图5. 传统时钟多路复用的裕量节省

如图5所示,随着电压降速率降低,潜在的裕量节省增加。较慢的速率使系统有更多时间响应并切换到安全频率,从而最大限度地实现潜在的电压和能耗节省。相反,较快的电压降速率会侵蚀潜在的节省。如图表所示,具有更快T_response和更低时钟插入时间的系统可以提高系统的能耗节省性能。

2.3.1 最大化最小电压(Vmin)节省

总体目标是减少电压过裕量,同时最大化性能并避免电压降引起的时序故障。上述分析提到了多种最大化潜在节省的方法(后续图表将进一步阐述):

- 减少T_detect—— 使用尽可能快的电压降检测器缩短检测时间。

- 避免使用过于激进的时钟缓解措施—— 除非绝对必要,否则不要采用二分频。

- 最小化T_prop_delay—— 电压降检测和时钟适应之间的紧密耦合解决方案非常有益,因为每个时钟周期都很关键。

- 减少时钟插入延迟—— 分布式时钟使时钟源更靠近相关电路。通过使用小型数字锁相环(PLL)实现此技术,同时支持以更精细的级别对模块进行独立时钟控制。

3.集成式电压降响应解决方案

集成式电压降响应解决方案包含两个组件:

- Aeonic Insight™ 电压降检测器

- Aeonic Generate™ AWM3

3.1 Aeonic Insight™ 电压降检测器

Aeonic Insight™ 电压降检测器是电压降检测器的全数字实现方案,具有灵活性和后硅可编程性。该电压降检测器通常以1G赫兹(GHz)至3G赫兹(GHz)的时钟采样周期工作,且具有后硅可编程阈值。这提供了调整和优化采样周期及精度的灵活性,进而优化电压降响应系统的潜在最小电压(Vmin)节省。

3.2 Aeonic Generate™ AWM3

Aeonic Generate™ AWM3是电压降缓解解决方案的核心组件,提供业界最快的响应时间T_response(不到两个周期),这是最大化最小电压(Vmin)节省的关键参数。AWM3可接收异步电压降断言输入,立即降低输出时钟频率且无毛刺。这一独特功能使AWM3能够最小化总适应时间T_adapt。如果无法接收异步输入,电压降断言信号必须与输出时钟域同步,这将大大增加T_adapt时间,并减少最小电压(Vmin)节省或可缓解的最大电压降。

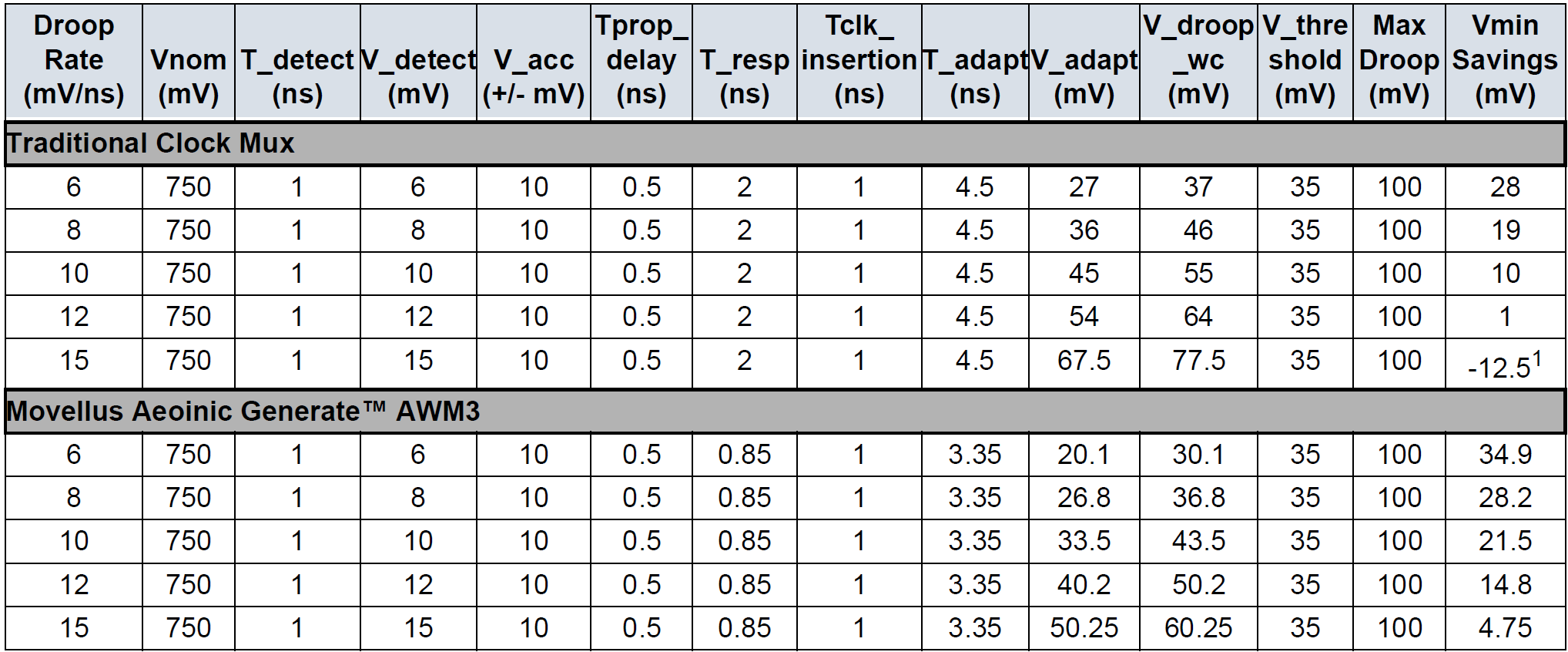

将AWM3与传统系统进行比较:如果电压降断言信号是异步的,必须将其锁存到系统时钟域,这至少需要1个时钟周期。如果时钟频率调整是在时钟源之间切换,无毛刺时钟多路复用器可能需要3个或更多周期,使T_adapt达到4个周期。如表2所示,这对电压降缓解响应有显著影响。

3.3 靶向电压降遥测

Aeonic集成式电压降响应系统拥有全面的可观测性套件,可集成到硅健康和监测分析平台中。在测试期间(包括任务模式和后硅调试阶段),可从该系统获取电压降持续时间和响应序列等输出数据。这些靶向指标可帮助用户精确调整其目标阈值和安全频率,以最大化电压裕量节省。表2展示了AWM3与传统时钟多路复用器之间的各种时序差异。

表2. AWM3与传统时钟多路复用器对比

¹ 此列中的负数表示在指定条件下无法缓解此类幅度的电压降。

表的前5行代表使用时钟多路复用器的系统,后5行代表使用AWM3作为时钟源的系统。Aeonic Insight™ 电压降检测器与Aeonic Generate™ AWM3的紧密耦合特性显著缩短了T_adapt时间并降低了V_adapt电压。请注意,两种场景均假设使用Aeonic Insight™ 电压降检测器。

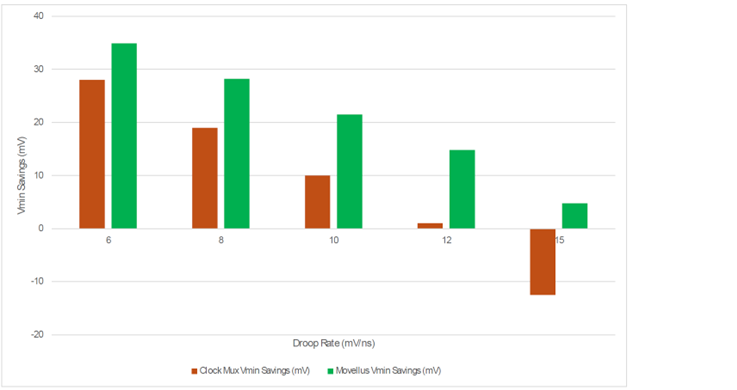

图6. 100毫伏(mV)电压降的最小电压(Vmin)节省对比

配备AWM3的系统可实现更大的最小电压(Vmin)节省,并且还能为更剧烈的电压降(本示例中高达15毫伏/纳秒(mV/ns))提供防护。值得注意的是,当电压降速率超过10毫伏/纳秒(mV/ns)时,传统时钟多路复用器方法无法提供有意义的最小电压(Vmin)节省;当超过12毫伏/纳秒(mV/ns)时,完全无法防护时序故障。

- 结论

本白皮书阐述了自适应时钟解决方案的关键要求,提供了电压降缓解解决方案的详细分析方法,并证明了由Aeonic Insight™ 电压降检测器和Aeonic Generate™ AWM3自适应时钟发生器组成的集成式电压降响应系统能够提供卓越的最小电压(Vmin)节省和电压降缓解效果。