COMET:芯片量产测试大数据分析工具

大数据挖掘是个非常热门的话题。集成电路行业里面有一个随时可见的大数据:芯片的量产测试数据。

几乎所有种类的芯片在出货之前,每一颗都需要经过几道的严格的测试,包括CP和FT测试。而每一道测试都会产生一系列的测试结果数据。因为测试程序通常是由一系列的测试项目组成,从各个方面对芯片进行充分检测,其结果不仅仅是告诉我们每颗芯片性能是否符合标准,更是能够给出各种详细数据充分定量地反应了每颗芯片从结构、功能到电气特性的各种指标。

当芯片出货量巨大的时候,所有这些产品的测试数据整合在一起,就能够在很大程度上反应出整个产品在设计和工艺制造上的一系列问题。这些问题很多是我们在实验室里通过对小批量产品进行分析所无法获得的。很多产品经验积累丰富的设计公司都非常重视对实际量产数据的追踪和分析,通过对数据充分分析利用往往能够找到产品目前在设计和生产工艺上存在的各种问题,从而帮助设计人员和工厂改善产品的性能和良率。

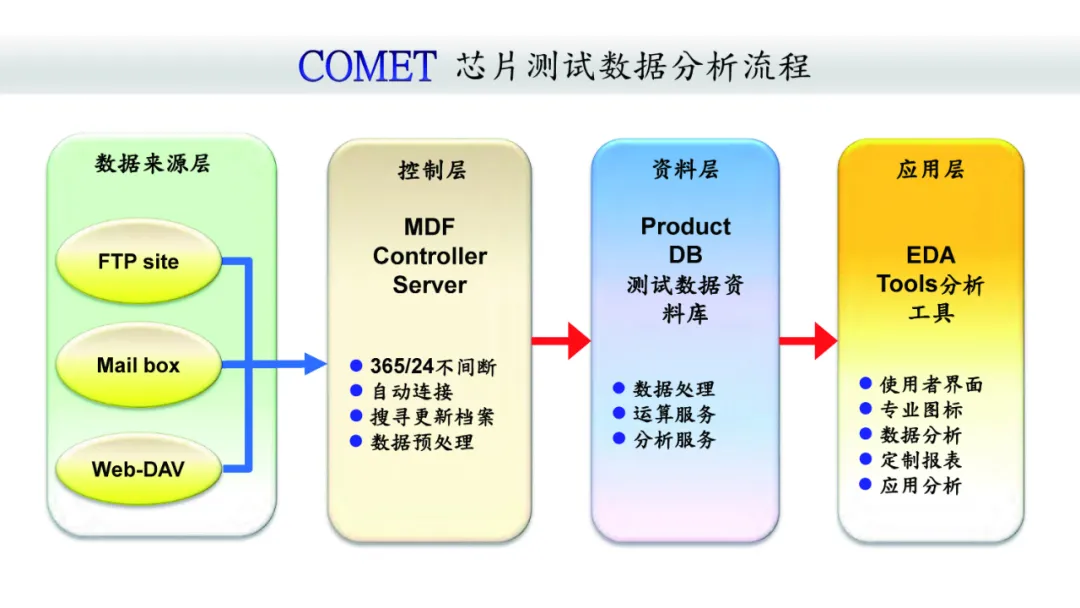

Comet 就是这样一款芯片测试大数据的分析解决方案,其可以部署于云端和企业内部的网络。专为「IC 设计公司」打造的IC 产品品质、良率与效能的工程管理方案,使IC设计公司更能专注于产品的开发与竞争力提升,进而提升IC 产品的设计与制造能力。

其采用最成熟的云端先进技术,提供客户可信赖的的技术服务,并且针对客户的需求,以敏捷的组件及报表开发,协助客户快速导入客制化的功能。提供多种应用的基本与扩充模块,随客户的业务变化调整方案:

Basic 方案:全方位的IC 产品工程管理与良率分析系统。

Premium 方案:三种扩充模块。

Premium-A:IC 电性测试参数之统计与质量分析模块。

Premium-B:Wafe r Bi n MA P 区域良率分析与编辑模块。

Premium -C:在制品 WIP 监控与数量分析模块

|

使用者工具 |

说明 |

用途 |

适用对象 |

|

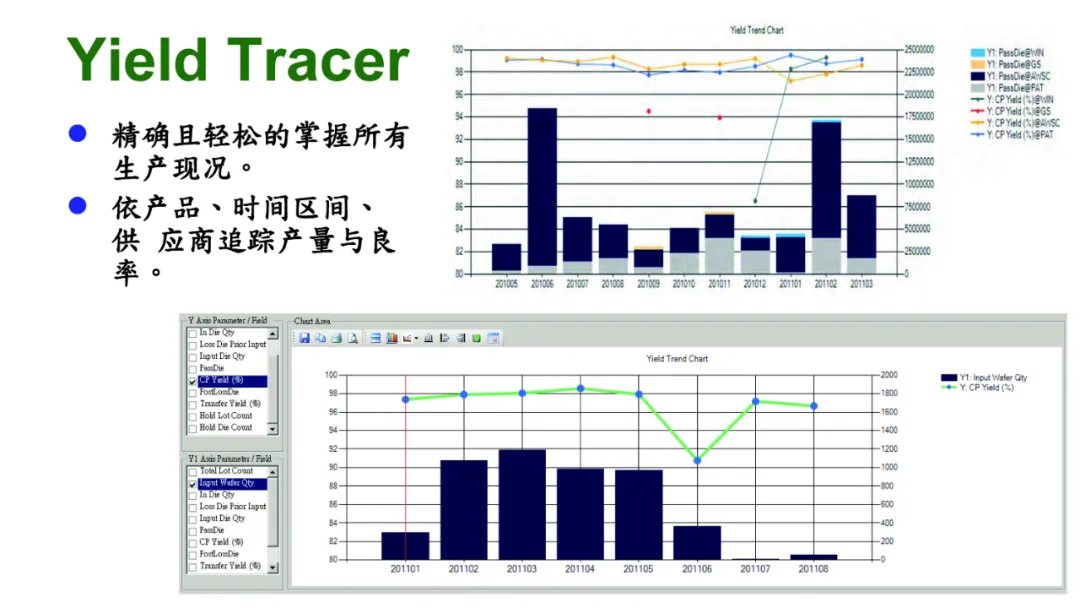

Yield Tracer |

提供公司产品现况监控与定 制化管理报表

|

平时追踪全公司产品良率及提供主管查阅的管理报表。 |

主管工程师 产品工程师 |

|

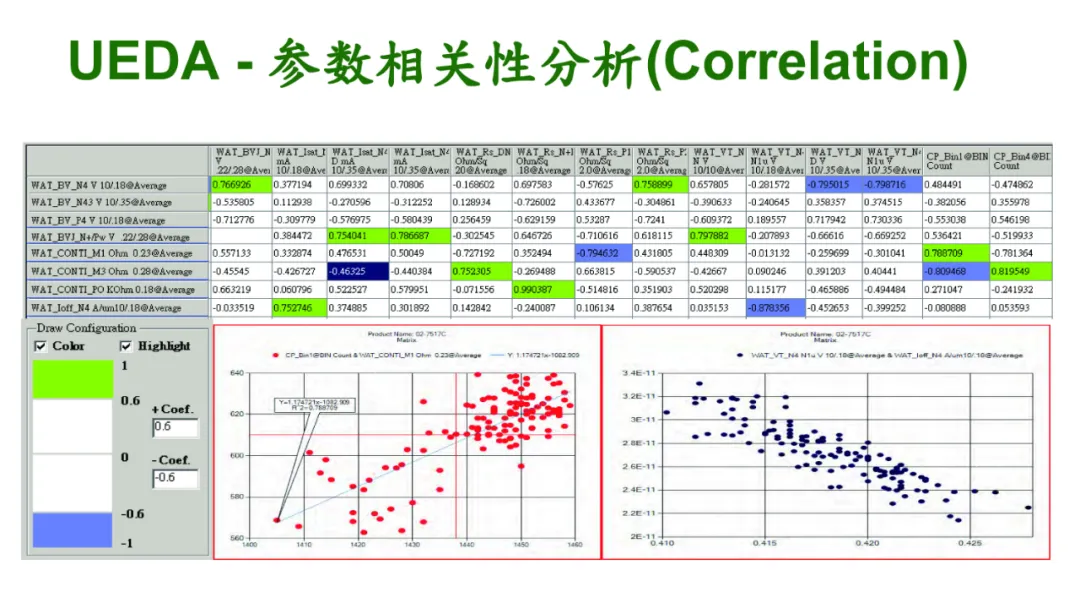

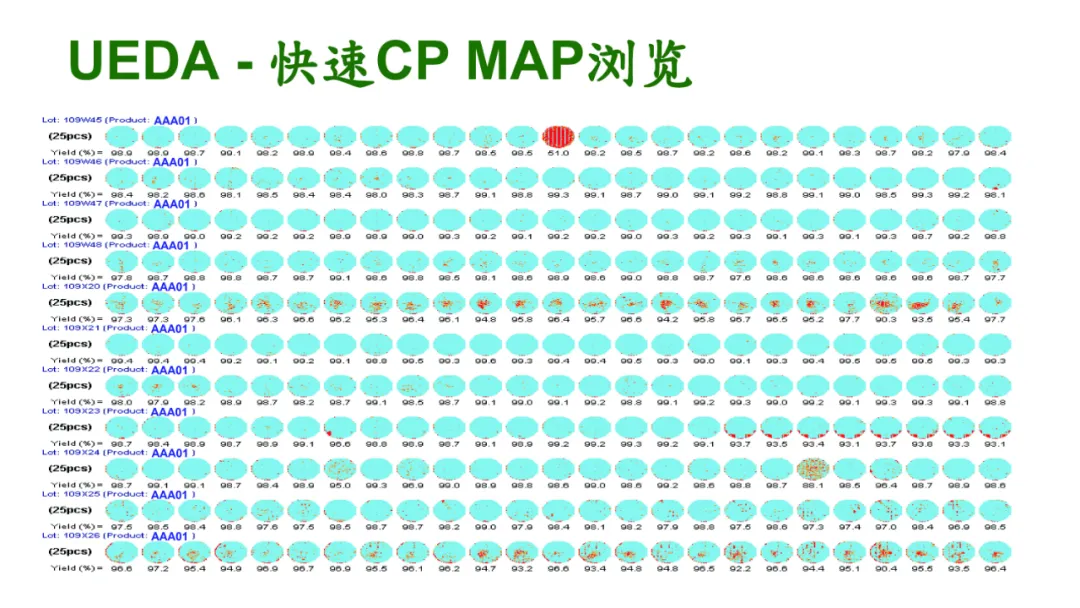

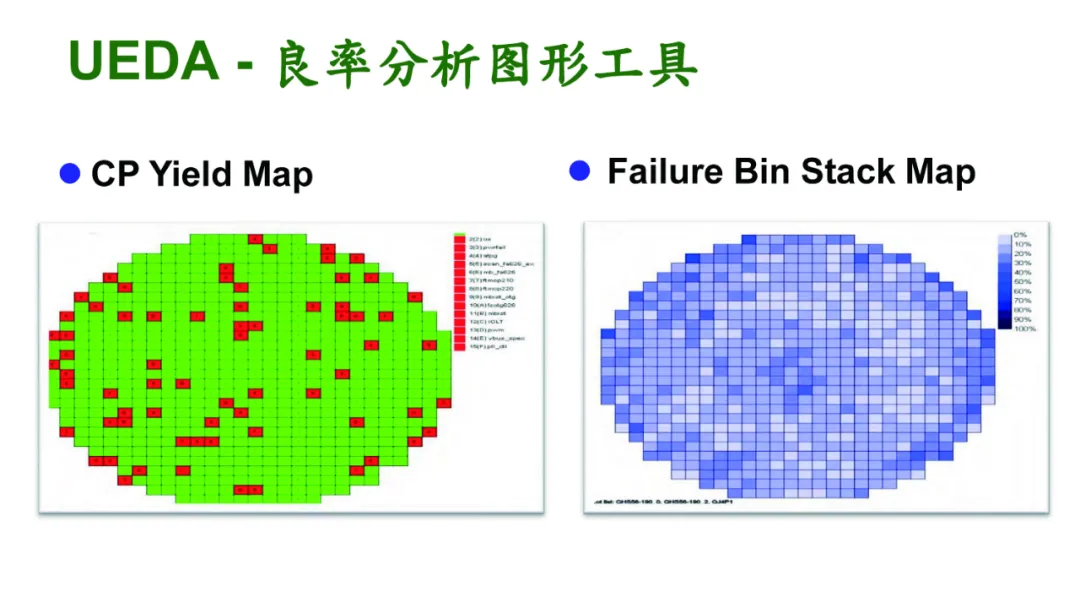

UEDA (Utility EngineeringData Analysis) |

提供产品各生产阶段之工程 数据查询,与良率与参数的 整合分析

|

适用于产品工程师查询工程资料,并针对良率与质量问题加以分析改善。 |

产品工程师 品管人员 |

|

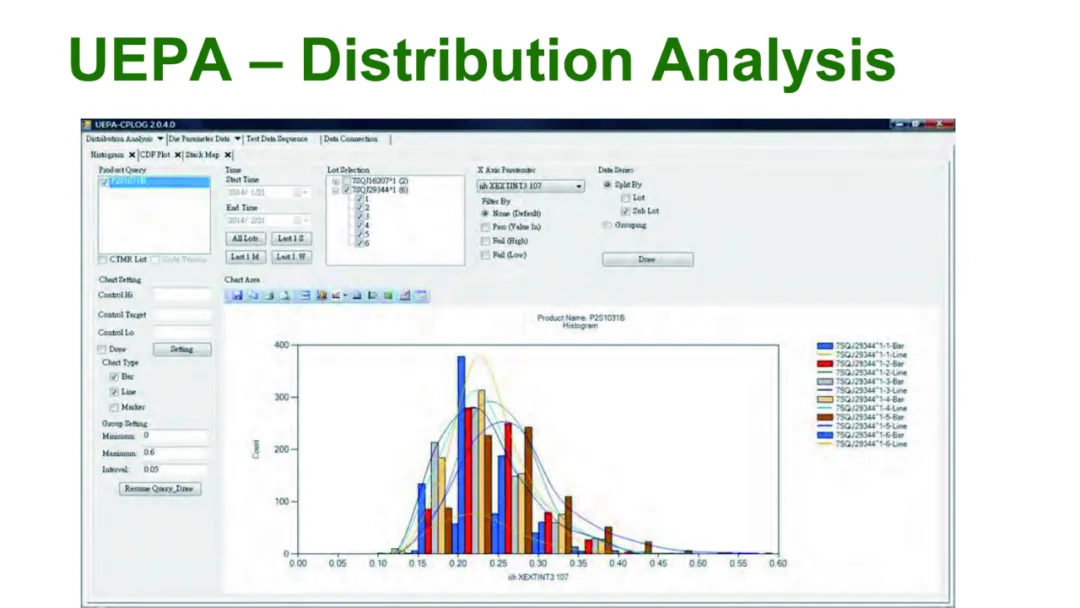

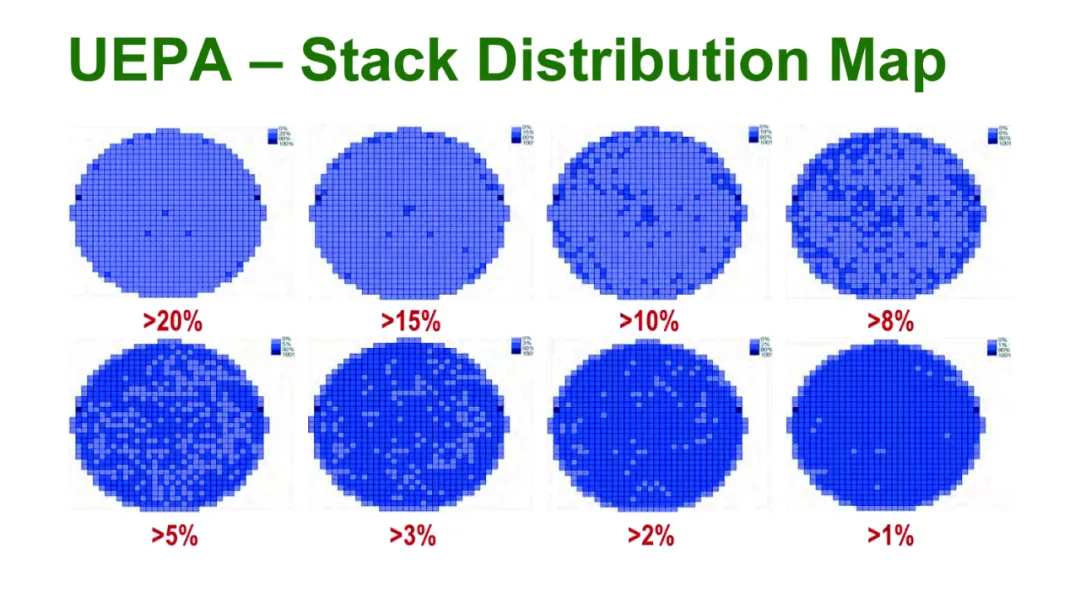

UEPA (UtilityEngineering ParameterAnalysis) |

提供产品最小测试单位的 各种测试参数之统计分析

|

深入分析测试参数之分布与统计值,并针对产品特性加以分析改善。 |

测试工程师 开发设计人员 |

Comet的方案使用流程简单,易于上手。

MDFC(Manufacturing Data FileController)服务器,是对产品制造与测试的各种数据,开发的数据整合自动化方案。

特色

-

将各种不同外站数据源、档案类别及内容格式,以任务排程的方式进行自动化。

-

建构产品的阶层式数据库,供信息查询、储存分类、以及其他应用分析所用。

-

客户可借由工具的服务,自动化整合所有与产品上下游相关的工程信息。

系统服务

-

应用服务器功能:常驻程序,自动登入、搜寻及下载。

-

服务程序:建立任务,排程执行,搜寻下载,格式转档,自动ID建立,存入数据库。

客户服务

-

提供客户各种数据撷取与转换的组件开发

-

依据应用与管理需求,客制所需报表。

-

规划所有产品信息流程及档案储存的自动化流程

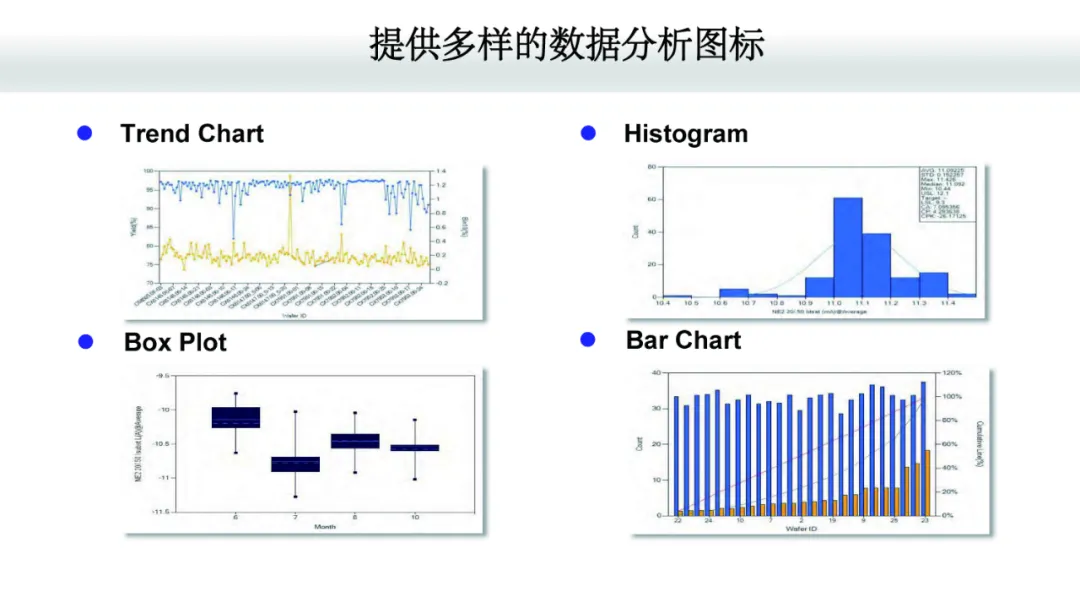

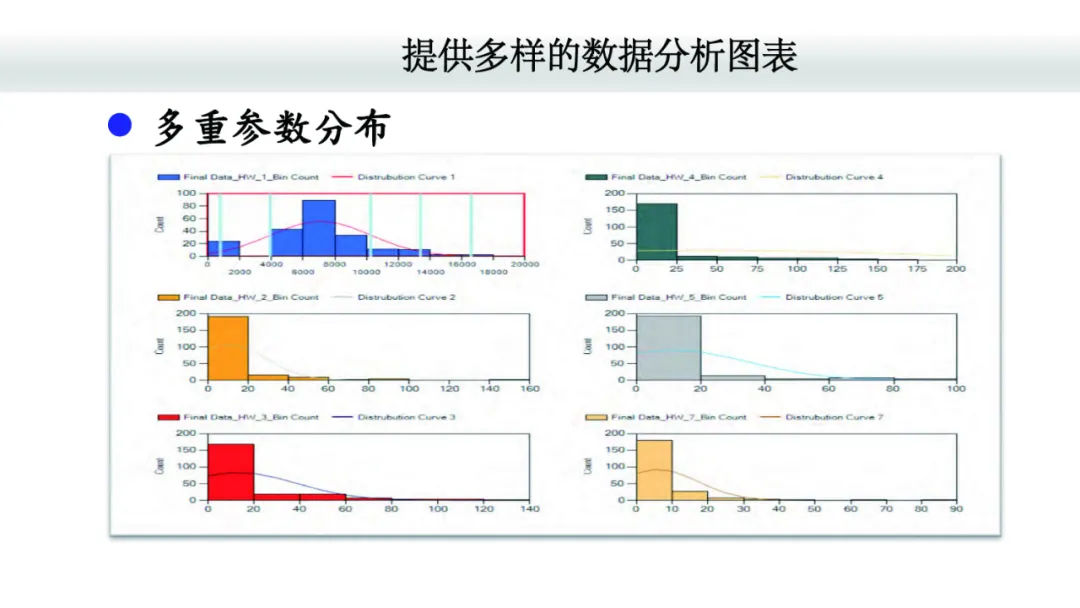

海量的测试数据导入数据库后,可以利用电脑端的应用程序,进行大数据的分析。